MOSFET

MOSFETは、Metal-Oxide-Semiconductor Field-Effect Transistor(電界効果トランジスタ)の略称である。

ゲートが(金属)-(酸化物)-(半導体)の構造を持つFETを指す。

FETの動作原理などもこちらに記す。

電気的特性

- 線形領域 \[ I_D=\beta((V_{GS}-V_T)-\frac{1}{2}V_{DS})V_{DS} \]

- 飽和領域 \[ I_D=\frac{\beta}{2}(V_{GS}-V_T)^2(1+\lambda V_{DS}) \]

- サブスレッショルド領域 \[ I_D\propto\beta\exp(\gamma(V_{GS}-V_T)) \]

\[ \beta=\frac{W}{L}\mu C_{ox} \]

基本構造

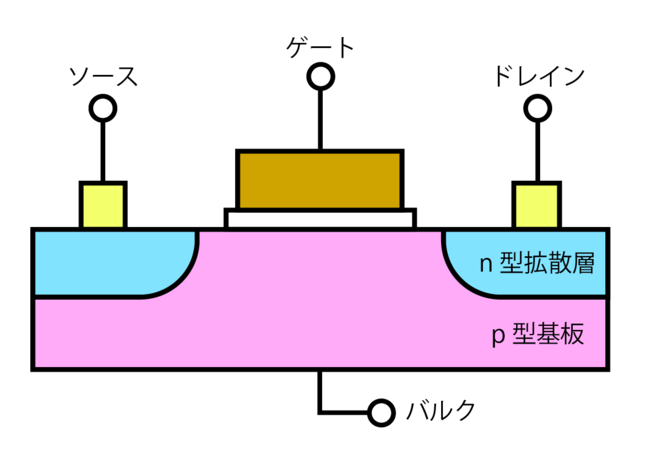

nMOSを例にMOSFETの基本構造を示す。

ゲート、ドレイン、ソース、バルクの4端子から構成される。

ゲート-バルク間の電圧(\(V_{GB}\),\(V_{G}\))で、ドレイン-ソース間の最大電流量(\(I_{DS}\))を制御することができる。

一般に、バルクとソース(もしくはドレイン)を接続するため、3端子として扱う場合も多い。

基本的なMOSFETはドレインとソースを逆向きにしても振る舞いは変わらない。

この2端子は動的に決まるものであり、電位が低い方をソースと定義している。

ゲート端子とp型半導体の間の酸化膜のことを、ゲート酸化膜と呼ぶ。

物質としては、

茶色...ポリシリコン、銅などの金属

黄色...銅などの金属

白色...酸化物

水色...n型半導体

桃色...p型半導体

で構成される。

大電流を制御するMOSFETのことを特にパワーMOSFETと呼ぶが、これはソースとドレインの対象性は持たない。

これはソース-ドレイン間にダイオードが挿入されているためである。

基本原理

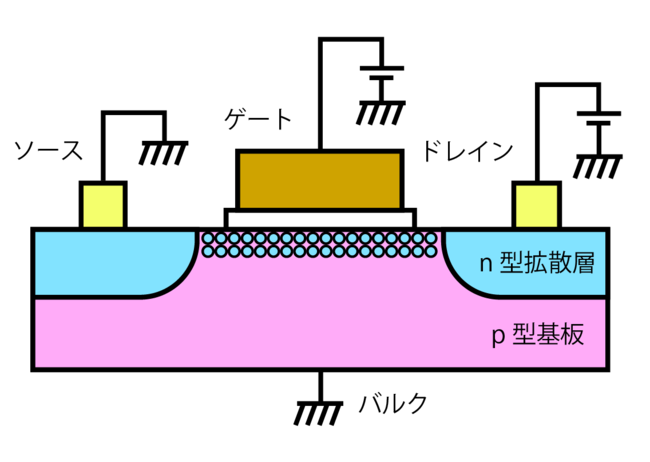

nMOSを例に基本原理を示す。

前提としてドレインをソースよりも高電位にする。

\(V_{GB}\)に電圧をかけていない場合には、ドレイン-ソース間のパスにおいてバルク-ソース間が逆バイアスとなるので、電流は流れない。

つまりは電流が流れないため、\(I_{DS}\)は0に近い。

\(V_{GB}\)に電圧をかけた場合には、ゲート-バルク間の電界によりバルクの酸化膜近辺に電子が貯まる。

この電子がドレイン、ソースのn型半導体をつなぐことにより電流が流せるようになる。

電子がつなぐパスのことをチャネルと呼ぶ。

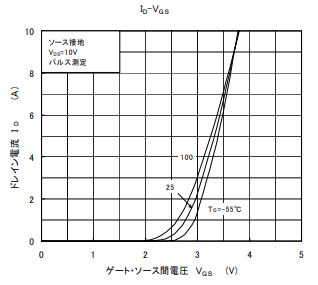

\(V_{GB}\)によって\(I_{DS}\)を制御できることをグラフに表すと以下のようになる。

例として2SK4017のデータシートを示す。

横軸が\(V_{GB}\)、縦軸が\(I_{DS}\)である。

\(V_{GB}\)を上げると\(I_{DS}\)が大きくなることがわかる。

ここで\(I_{DS}\)が流れ始める時の電圧をスレッショルド電圧(閾値電圧)と呼び\(V_{th}\)で表される。

MOSFETの種類

MOSFETは\(V_{th}\)の値により2種類に分類される。

- エンハンスメント型 \(V_{th}>0\)のMOSFETを指す。

- デプレッション型 \(V_{th}<0\)のMOSFETを指す。

\(V_{GB}=0\)のときは電流が流れない。

E型、normally off型もと呼ばれる。

\(V_{GB}=0\)のときも電流が流れる。

D型、normally on型もと呼ばれる。

特性によるFETの分類

IV特性

CMOS回路

MOSFETを組み合わせることにより、論理回路を実現することができる。

その一般的な方法としてComplimentary MOS回路、略してCMOS回路と呼ぶ。

Complimentaryとは相補的という意味で、pMOSとnMOSをそのように使うことから名付けられた。

遅延

消費電力

消費電力は2種類に大別される。

- ダイナミック電力

- スタティック電力

ダイナミック電力

ダイナミック電力とは、ゲートがスイッチしたときに消費される電力のことを指す。

これの大部分はスイッチング電力である。

そのほかは貫通電流による電力消費がある。

スイッチング電力

CMOS回路のスイッチングにより発生する電力であり、負荷容量の充放電によって消費される。

スイッチング電力は次式によって表される。

\[

P_{switching}=\alpha {CV_{DD}}^{2}f

\]

\(\alpha\)...スイッチング確率

\(C\)...負荷容量

\(V_{DD}\)...電源電圧

\(f\)...クロック周波数

スイッチング確率はアプリケーションに大きく依存する。

負荷容量は、ゲート容量、拡散容量、配線容量の3つによって決定される。

貫通電流

貫通電流とは、nMOSとpMOSが同時にVthを超えた場合に発生する電流である。

これは、入力信号の立ち上がりが遅いことによって起こる場合がある。

スタティック電力

トランジスタがオフの状態での消費される電力を指す。

90nmプロセス以前はダイナミック電力に比べてこれは小さかったために無視されてきたが、微細化が進むに連れ指数関数的に増加した。

スタティック電力の要因としては以下の4つが挙げられる。

- サブスレッショルドリーク電流

- ゲートリーク電流

- 接合リーク電流

- 競合電流

サブスレッショルドリーク電流

ゲートリーク電流

接合リーク電流

競合電流

集積回路

集積回路とは、MOSFETの集合体である。

前述(まだい書いてない)したCMOSを構成することにより、様々な論理回路、はたまたCPUを実現している。

集積回路の発展は微細化によって進められている。

微細化進歩の目安として、ムーアの法則が挙げられる。

ムーアの法則とは、「チップに集積される素子数は3年で4倍のペースで増大する。」というものである。

各社がこの法則を目安に競合を繰り返したため、結果としてこの法則に準じた。