低消費電力化技術

半導体デバイスにおいて能力向上を目指す上で障害となるのが、電力消費の増加である。

消費電力が増える原因については別にて。

また消費電力を考える上では、どこで電力が消費しているのかを抑えておくと理解が早い。

クロックゲーティング

クロックゲーティングは、ダイナミック電力、特にスイッチング電力を抑制する手法である。

現在、汎用のCPUにも適応されている技術である。

前提として、スイッチングを行うと消費電力が増えてしまう。

これは、ダイナミック電力の大部分を占めるスイッチング電力は

\[

P_{switching}=\alpha CV_{DD}^{2}f

\]

で表され、スイッチング確率\(\alpha\)に比例するためである。

クロック信号とは、別の言い方をするとスイッチング確率\(\alpha\)が100%の信号と言える。

このため、無駄にクロック信号を処理してしまうと消費電力の無駄が大きいと言える。

クロックゲーティング(Clock Gating:CG)とは、伝送ゲートやマルチプレクサを用いて、必要としていないところには送らないようにする、つまりはゲートする技術を指す。

パワーゲーティング

パワーゲーティングは、スタティック電力全般を抑制する技術である。

こちらは比較的簡単な考え方で、演算に使用していないところには電力を与えないようにする技術である。

電力をゲートするので、パワーゲーティング(Power Gating:PG)である。

本ページではPGと略されることがある。

パワーゲーティングを適用する事によって、スタティック電力を削減することができる。

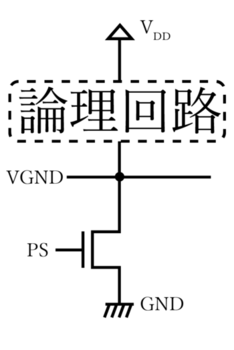

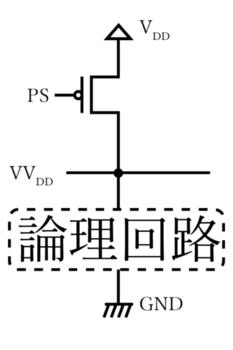

パワーゲーティングは、具体的には論理回路と電源線、もしくはグラウンドの間にパワースイッチ(Power Switch:PS)と呼ばれる高閾値のトランジスタを挿入することにより、論理回路を使用しないときには電気的に遮断するものである。

パワーゲーティングは、パワースイッチをどこにつけるかで2種類存在する。

フッタ型パワーゲーティング

フッタ型PGは、論理回路とグラウンドの間にPSを挟む構造のものである。

PSには、グラウンド電位を伝達したいため、nMOSを使用する。

ヘッダ型パワーゲーティング

ヘッダ型PGは、論理回路と電源線の間にPSを挟む構造のものである。

PSには、電源電位を伝達したいため、pMOSを使用する。

180-90nmプロセスではフッタ方式、45nmプロセスからはヘッダ方式が用いられている。

これは、pMOSがnMOSよりもリーク電流が少ないことが考慮されたためである。

なぜpMOSのほうがリーク電流が少ないのかはこちらから。

パワーゲーティングをどこに行うかというのは非常に大きなファクターである。

特に注意すべきなのが、揮発回路に適用した場合である。

揮発回路は、SRAMを代表とする電源を遮断するとデータや動作が保持できない回路のことである。

これらにもPGを適応するために、不揮発性の素子を使い、元の状態を復元できるようにするという手法が取られている。

一般にこれを不揮発性パワーゲーティング(NonVolatile Power Gating:NVPG)と呼んでいる。

SOI

超低電圧化

超低電圧化は、主にダイナミック電力のスイッチング電力を抑制しようとする技術である。

クロックゲーティングでも説明したとおり、スイッチング電力は次式で求められる。

\[

P_{switching}=\alpha CV_{DD}^{2}f

\]

ここて着眼すべきなのは、電源電圧の2乗に比例することである。

したがって、低電圧化しスイッチング電力、もといダイナミック電力を減少させようという技術である。

では、電源電圧はどれだけ下げることができるのだろうか。

感覚的にはスレッショルド電圧である\(V_{th}\)のような気がするが、実はそうではない。

この\(V_{th}\)よりも低い電源電圧でドライブさせている。

これを理解するには新しい特性を知る必要がある。

新しい特性とは、サブスレッショルド電流\(I_{sub}\)というものである。

\(V_{th}\)以下では電流が流れないと(別記事にて)前述したが、実はここにもほんの少しの電流が流れているのである。

それがこの\(I_{sub}\)である。

この\(I_{sub}\)は次式によって求められる。

\[

記述中

\]

つまりは、この\(I_{sub}\)を\(V_{gs}\)(正確には\(V_{gb}\))により変化させることができるということである。